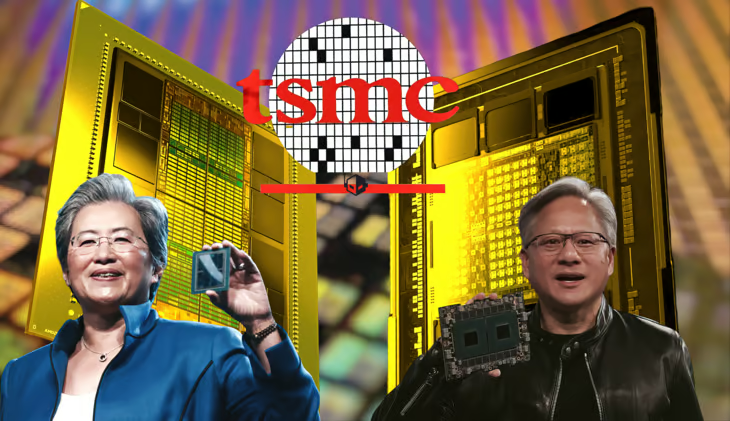

대만 반도체 제조회사(TSMC)가 특히 AI 분야에서 최첨단 칩에 대한 수요가 강한 가운데, 자사의 첨단 3nm 및 5nm 반도체 제조 공정과 CoWoS 첨단 패키징 기술에 대한 가격을 3%-5% 인상할 계획인 것으로 알려졌습니다.

TSMC 3nm 및 5nm 가격 인상

최신 보고서에 따르면 TSMC는 첨단 3nm 및 5nm 반도체 제조 공정의 가격을 3-6% 인상할 계획이라고 합니다. 이 가격 인상은 회사가 2025년과 2026년까지 3nm 용량을 거의 완전히 활용하고 있는 시점에 이루어졌습니다. 이 인상은 최첨단 칩 기술에 대한 높은 수요, 특히 빠르게 성장하는 AI 부문에 대한 높은 수요를 반영합니다. TSMC의 지배적인 시장 지위 덕분에 Apple과 NVIDIA와 같은 유명 고객에게 주요 공급업체로 남아 있기 때문에 이러한 가격 조정을 구현할 수 있습니다.

CoWoS 포장 가격 인상

첨단 패키징 기술, 특히 Chip-on-Wafer-on-Substrate(CoWoS)는 5-10%의 상당한 가격 상승을 보일 것으로 예상됩니다. 이러한 가격 상승은 특히 AI 애플리케이션에서 칩 성능을 향상시키는 데 있어 첨단 패키징의 중요성이 커지고 있음을 반영합니다. TSMC의 패키징 용량은 올해 3분기까지 거의 두 배로 증가하여 현재 17,000개에서 월 33,000개의 웨이퍼에 도달할 것으로 예상됩니다. 주목할 점은 TSMC의 첨단 패키징 용량의 약 절반이 NVIDIA 제품에 전념하고 있으며, AMD가 두 번째로 큰 고객입니다. 패키징 수요는 내년에 약 600,000개의 웨이퍼에 도달할 것으로 예상되며, 이는 TSMC의 530,000개 용량을 초과하여 가격 상승을 더욱 정당화합니다.

가격 인상 이유

TSMC의 첨단 제조 공정 및 패키징 기술의 가격 인상은 여러 요인에 의해 결정됩니다.

- AI 칩에 대한 강력한 수요로 인해 2025~2026년까지 3nm 용량이 거의 완전히 활용될 것으로 예상

- 지속적인 공급망 제약으로 인해 용량 확장에 대한 상당한 투자가 필요합니다.

- AI GPU 성능에 필수적인 고급 패키징은 수요와 공급의 불일치에 직면해 있으며 2025년에는 수요가 웨이퍼 용량을 70,000개 초과할 것으로 예상됩니다.

- TSMC의 지배적인 시장 지위는 고객 기반을 유지하면서도 가격을 조정할 수 있게 해줍니다.

이러한 증가는 AI 기반 기술 분야에서 최첨단 반도체 기술의 중요성이 커지고 있으며, TSMC가 생산 능력 투자와 수익성 사이에서 균형을 맞춰야 할 필요성을 반영합니다.

고객 및 제품에 미치는 영향

TSMC의 첨단 제조 공정 및 패키징 기술에 대한 예상 가격 인상은 기술 산업에 파장 효과를 미칠 가능성이 높습니다. Apple, NVIDIA, AMD와 같은 고객은 더 높은 생산 비용에 직면할 수 있으며, 이는 스마트폰, 컴퓨터, AI 하드웨어와 같은 최종 제품의 가격 인상으로 이어질 가능성이 있습니다. 그러나 최첨단 칩에 대한 강력한 수요, 특히 AI 부문의 수요를 감안할 때, 대부분 고객은 TSMC의 첨단 제조 역량에 대한 액세스를 확보하기 위해 이러한 비용을 흡수할 것으로 예상됩니다. 이러한 상황은 빠르게 진화하는 AI 및 컴퓨팅 환경에서 혁신과 성과를 주도하는 데 있어 TSMC 기술의 중요한 역할을 강조합니다.

뉴스 출처:

최신 블로그 게시물을 업데이트하려면 구독하세요

댓글을 남겨주세요: